Intel's 2024 PC Chips Getting a Speed Boost From New Power Tech - CNET

Intel’s Arrow Lake processor for 2024 PCs will get a speed boost thanks to a new technique sending electrical power through its chips.

In tests detailed Monday, Intel said a technology it calls PowerVia offered a 6% speed boost on test chips. Another big change called RibbonFET that’s coming with Arrow Lake should offer further advantages.

That’s a big deal for Intel, which has struggled to reclaim a once formidable chipmaking advantage that it lost to Taiwan Semiconductor Manufacturing Co. (TSMC) and Samsung. Those two companies are “foundry” companies that make other chips, notably Intel’s top competitors: Apple, AMD, Nvidia and Qualcomm, but they aren’t expected to match PowerVia until later.

If PowerVia and RibbonFET arrive on time in 2024 with the Intel 20A manufacturing process, then are improved with 18A in 2025, it could help Intel better match rival chips when it comes to packing in lots of circuitry and running efficiently to extend battery life. Apple’s MacBook laptops run unplugged for hours, and many models completely do away with a cooling fan to keep their chips from overheating.

“It looks like a good incremental step,” but not a permanent advantage for Intel, Tirias Research analyst Kevin Krewell said of PowerVia. “Everybody’s going to follow suit and will have the same technology in place over time.”

And because Intel is trying to become a foundry too, it could mean some of those competitors actually could become customers that, like Intel’s own chips, benefit. Intel missed out on making smartphone chips, but in Intel’s ideal future, it could be building the Apple processor that powers a future iPhone.

Meet backside power delivery

Chips process data and perform calculations using tiny electrical switches called transistors that can switch on and off billions of times per second. Today, the necessary power to do that comes on equally tiny electrical links that wind their way through a complex 3D labyrinth of wires that also carry instruction signals to the transistors.

But with Arrow Lake, the 2024 successor to this year’s Meteor Lake processor for PCs, Intel will separate the power delivery from the communication links, moving it to the opposite face of the chip. In the semiconductor industry, it’s called a backside power delivery network, but Intel calls its version PowerVia.

“PowerVia is a revolutionary change for on-chip interconnects that improves power, performance, area, and cost,” all important dimensions of transistor design, said Ben Sell, an Intel vice president who worked on the technology.

Problems with manufacturing progress

By incorporating PowerVia in its highest volume, highest profile processor, Intel is counting on backside power delivery working well and not degrading manufacturing with flawed chips. To guard against that possible disaster, Intel developed PowerVia using test chips built with its current Intel 4 manufacturing process, used to make elements of Meteor Lake. It works well enough that it’ll be standard for Intel 20A and its successor, 18A.

PowerVia is a crucial element to Intel’s recovery effort. In the relentless effort to miniaturize transistors, to keep pace with Moore’s Law, Intel faltered a decade ago and hasn’t fully recovered. Although Samsung and TSMC are working on backside power delivery, PowerVia could beat it to market. For example, TSMC’s backside power technology isn’t expected until 2026.

“From everything we know, this is coming a node ahead of what the industry is doing and gives our customers the advantages of PowerVia as soon as possible,” Sell said. A node is a major step in chip manufacturing technology.

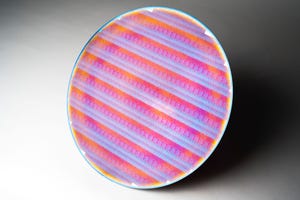

PowerVia adds new processing steps to the hundreds already required to make a chip. Once the transistors are carefully built on the front of a silicon wafer of chips, the wafer must be flipped over, ground thinner, polished, and have power connections installed.

That adds cost and time. But removing the power lines from the front of the wafer means there’s more room for communication links, simplifying designs and overall lowers manufacturing costs.